Overscan

Techniques

Part II

Shifts of the Useable Screen

In the usual non-overscan scenario, DE is activated and

disactivated 16 pixels before and after each line of the useable

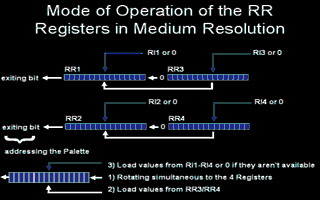

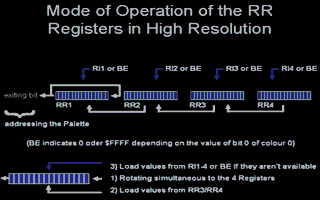

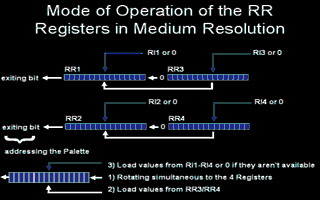

screen. The SHIFTER will only display the four IR values once it

has received all of them. But if some of the IR registers were

already filled, it won't need to wait to load all of them before

loading the RR registers. Since the RR registers are loaded

earlier, the useable screen will be shifted left. This shift

will correspond directly to the number of words less that it did

not need to wait for. As we saw, the MMU sends a new word to the

SHIFTER every 500ns. Thus if only IR1 were filled, the image

would be shifted 500ns left (corresponding to 4 pixels in low

resolution). IR1 and IR2 correspond to 8 pixels, and so on.

Note that this effect is perpetuated from VBL to VBL: if at the

end of a VBL, the IR registers are not all empty, the next

useable screen will be shifted left. If one changes resolution

during the useable screen, depending on the location of the

change, it is possible to affect the normal functioning of the

IR registers. Such changes of resolution can result in the

bitplanes being shifted. Finally this description is incomplete,

because it does not account for screens where one observes

alternating bands of useable screen and border.

Consider now a line with the left border removed: it contains

186 bytes, or 92+1 words. 92 is a multiple of 4, so there is a

word too many per line. As we know, the beginning of the right

border is due to DE being disactivated, so its position will not

vary: if there is one word too many per line it will be loaded

on the left of the screen. As the SHIFTER displays border unless

all IR registers have been loaded, the first line displayed will

stop 500ns before a normal line would, i.e. 4 pixels left in low

resolution. At the end of the first line IR1 is already loaded,

so the second line should start 0.5us earlier. Similarly at the

end of the second line both IR1 and IR2 are already loaded, so

the third line should start 1us earlier. Thus in low resolution

one would expect the following sequence of left shifts: 4-8-12-0

pixels. This actually occurs rarely (one time out of 20),

depending on power up conditions causing the the GLUE, MMU and

SHIFTER to be slightly out of synch. Instead one usually obtains

the truncation of line four pixels early corresponding to the

disactivation of DE. Is IR1 ignored? Indeed at the beginning of

each left overscan line there is a transition to high resolution

for a few cycles to activate DE. The change to high resolution

occurs before DE is activated. Then there are 500ns before the

Load/Dcyc signal of the MMU is activated (because there are 94

positions between the switch to monochrome and the switch to

60Hz to remove the right border: that is to say when DE is

usually disactivated, for 93 (92+1) words read by the MMU). The

fact that DE is activated, but Load/Dcyc isn't has as effect to

clear the last IR register loaded, and to decrement the

Number_of_read_bitplanes register. Thus if the MMU responds

earlier, which can happen if it is out of synch with the

SHIFTER, one will obtain the expected sequence of 4-8-12-0 pixel

shifts in low resolution. To conclude, left overscan alone is

potentially unstable and it is unadvisable to use it alone.

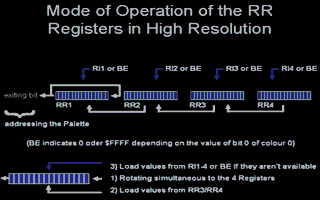

So why is right overscan stable? Each line is two words too

long! In fact, right overscan is only relatively stable in 50Hz

low resolution: in medium resolution, two words too many

correspond to 16 pixels. As all the IR registers must be loaded

before their contents is transfered to the RR register, every

second line is shifted left 16 pixels. Similarly, at 60Hz in low

resolution the same thing occurs with an 8 pixel left shift

every second line: only IR3 and IR4 need to be loaded. The fact

this does not occur at 50Hz means that Number_of_read_bitplanes

must be reset to zero. The same effect occurs for 158 byte

lines: they should be shifted by 12-8-4-0 pixels every 4 lines

in low resolution, since they have 3 words too many. These

anomalies are due to rare combinations of the DE and Load/Dcyc

signals as in the case of the left border: Load/Dcyc is active

when DE is disactivated, or DE is active while Load/Dcyc have

not been activated in the last 500ns.

|